# A Technique for Improving Input Current Zero-crossing Distortion of Boost PFC Converters for Airborne System

Bin Zhou<sup>1</sup>, Hongtao Shan<sup>2</sup>

<sup>1</sup> (College of Mechanical Engineering, Shanghai University of Engineering Science, Shanghai, China)

<sup>2</sup> (College of Electronic and Electrical Engineering, Shanghai University of Engineering Science, Shanghai, China)

**Abstract :** In airborne AC power system, input current may distort at the vicinity of input voltage zero crossing in Power Factor Correction (PFC) converter. This paper is analyzed the essential causes of the zero-crossing distortion and points out that the major causes are the value of inductor and the phase displacement between input current and input voltage. By adopting parallel interleaving technique, it can decrease the inductor and increase the equivalent switching frequency, improve input current zero-crossing distortion effectively. The effectiveness of this method is verified by simulation and experiments. The experiment results are demonstrated that it can make input current harmonics meet relevant standards so it can be applied in airborne system.

Key words- Airborne System; Zero-crossing Distortion; Value of Inductor; Phase Displacement; Parallel Interleaving

#### I. INTRODUCTION

In modern power electronics technology, Power Factor Correction (PFC) technology has been studied and applied widely. The input current is tracked with the input voltage strictly by the control circuits in PFC converters, so as to improve the power factor and suppress harmonic currents effectively. However, with the increase of the input frequency, the phenomenon of input current zero-crossing distortion would occurs, and the higher the input frequency is, the distortion phenomenon will be more serious <sup>[1]</sup>. The airborne AC power system is 115V/400Hz, the distortion phenomenon is more obvious in this high-frequency and the THD is higher. It is faced with much difficulty to meet the harmonic current standard GJB181B-2012<sup>[2]</sup> in airborne system.

Single-phase PFC converter input current is ahead of the input voltage <sup>[3]</sup>, and when the input frequency increases, the phase difference is increased accordingly, so near the input voltage zero crossing, input voltage and input current presence reverse. When the current is going to change, the result of one-way bridge rectifier diode conductivity is clamped to 0, waits until the input voltage starts to change direction, thus generating a current instantaneous step, generating zero-crossing distortion phenomenon.

Now researchers have proposed some solutions such as phase delay, the duty feedforward and so on. In some papers, by modeling the Boost PFC converter, the author added one voltage feed-forward network (LPAC) in the current control loop to reduce current phase advance. However, the whole design is more complex, and the phase difference is not the only reason so the control effect isn't obvious. The new structure of bridgeless topology is complex and difficult to control. What's more, the EMI problems are difficult to be solved effectively. This article focuses on the reasons of the zero-crossing distortion in Boost PFC converter, proposes a new method which is parallel interleaving technique to improve the zero crossing distortion, and uses simulation

software to demonstrate the theoretical analysis. Finally, the feasibility of this method is demonstrated by experiments.

#### **II. THE REASONS OF THE ZERO-CROSSING DISTROTION**

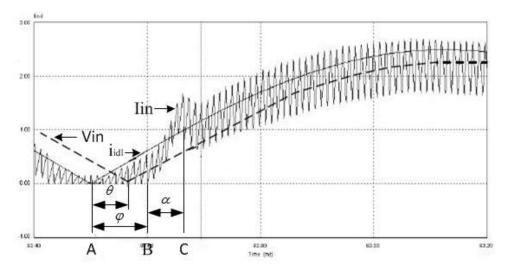

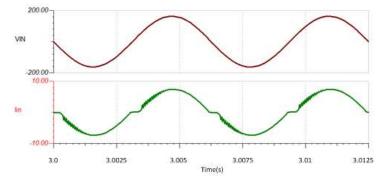

Assuming Boost PFC converter input voltage is  $V_{in} = V_m \sin(2\pi ft)$ , where  $V_m$  is the input voltage amplitude, f is the frequency of the input power. Ideally, Boost PFC converter input current is sinusoidal and in phase with the input voltage. By modeling the Boost PFC converter, it indicates that the input current phase is ahead of the input voltage and the higher the input higher the frequency is, the greater the retardation is<sup>[4]</sup>. Assuming the phase difference is<sub> $\theta$ </sub>, ideally  $i_{idt} = \text{Im} \sin(2\pi ft + \theta)$ . Input current distortion process is shown in Figure 1:

Figure-1: The input current distortion process

#### 2.1 The converter operating in DCM mode

In the horizontal axis of AB interval, the converter operates in discontinuous mode. When the current is interrupted, the power gain level is lower than the one of continuous current, causing the gain of the current loop reducing, so that the input current is slow to respond, the inductor current is difficult to track the reference current. Supposing the DCM mode continues angle is  $\varphi$ , in the discontinuous mode boundary:

$$\begin{cases} \Delta I = \frac{(V_0 - V_{in})(1 - D)}{L \cdot f_s} \\ \Delta I = 2I_0 / (1 - D) \end{cases}$$

(1)

Simultaneous equation and replace  $\pi$ - $\varphi$  to  $2\pi$ ft, simplification is:

$$(V_0 - V_m \sin \varphi) \cdot V_m \sin \varphi = 2V_0 L f_s \cdot I_m \sin(\varphi - \theta)$$

<sup>(2)</sup>

Order one function:

$$y_1(\alpha, f_s, \theta, L) = (V_0 - V_m \sin \varphi) \cdot V_m \sin \varphi - 2V_0 L f_s \cdot I_m \sin(\varphi - \theta)$$

(3)

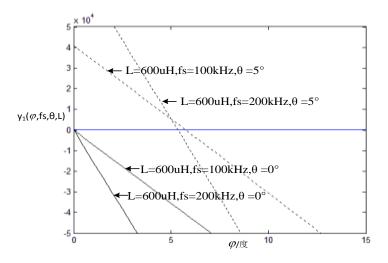

The function corresponding to the abscissa point is  $\mathcal{P}$ , Figure 2 depicts a graph of relationship graph

when  $\theta = 0^{\circ}$ ,  $\theta = 5^{\circ}$ ; fs=100kHz, fs=200kHz (when the specific parameters is  $V_m = 163V$ ,  $V_o = 390V$ , Im = 10A). As can be seen from the figure, along with the increase,  $\varphi$  is also growing, and within range, the converter operates in DCM mode. After the increase of the switching frequency,  $\varphi$  is

significantly reduced. In order to reduce the converter operates in discontinuous mode of time,  $\theta$  should be reduced and increase the switching frequency.

Figure-2: The Relationship Between  $\varphi$  and  $\theta_s$  fs

# 2.2 Cusp distortion

Seen in Figure 1, when the intermittent mode is ended, the inductor current sharp rise, there is a clear transition from B jump into C, at this stage the actual input current curve deviates from the ideal current track. Supposing the angle of cusp distortion is  $\alpha$ , at this time on the ideal input current to derivate to obtain the desired increase in slope:

$$\frac{di_{idl}}{dt} = 2\pi f \cdot \operatorname{Im}\cos\left(2\pi ft + \theta\right) \tag{4}$$

Obviously, the higher the power input frequency is, the rising slope converter needed is greater, so cusp distortion with increasing input frequency becomes more and more serious. According to Boost PFC circuit  $di_L/dt = V/L$ , at this time Boost PFC converter can provide for the inductor current rise rate is:

$$\frac{diL}{dt} = V_{\rm m} \sin(2\pi ft) / L \tag{5}$$

From Equation (5) it can be seen, the current rise rate that the converter provides is regardless of the input frequency, only a sense of the value of inductor. The smaller the inductance is , the rising slope the converter provides is greater so it will be better able to track the input current over current curves. Integrate Equation (5), and order  $i_L = i_{idl}$ , the needed angle  $\alpha$  that the inductor current tracking over ideal current is:

$$V_m(1-\cos\alpha)/2\pi fL = \operatorname{Im}\sin(\alpha+\theta)$$

(6)

According to equation (6), order one function:

$$y_2(\alpha, f, \theta, L) = \frac{V_m(1 - \cos \alpha)}{2\pi f L} - \operatorname{Im} \sin(\alpha + \theta)$$

(7)

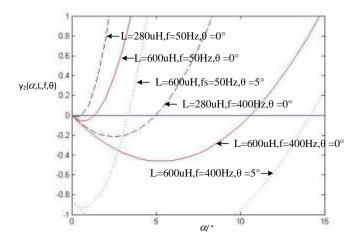

Function  $y_2(\alpha, f, \theta, L) = 0$  corresponding to the abscissa point is that the function of the image as shown in Figure 3.As can be seen from the figure, when the input frequency is 50Hz, with an increase from 0 ° to 5 ° of  $\theta$ , the  $\alpha$  values are 1.5 ° and 3 °. When the input frequency increases to 400Hz, under the same circumstances,  $\alpha$  becomes 10.5 ° and 14 °.  $\alpha$  will increase as  $\theta$  and f increase. But when the value of inductor reduces from 600uH to 280uH,  $\alpha$  is down from 5 ° to 0.5 °. Thus at high input frequencies, in order to improve the current waveform, it is necessary to reduce  $\alpha$ , so the value of inductor can be reduced to improve  $di/dt_{\circ}$

Figure-3: The Relationship Between  $\alpha$  and  $L_{\gamma}$   $\theta_{\gamma}$  f

### **III. The INTRODUCTION OF PARALLEL INTERLEAVING TECHNOLOGY**

From the above analysis, to reduce the zero-crossing distortion, it is need to reduce L and reduce  $\theta$ . The value of the inductor is subject to the ripple current so it can't be reduced too much, otherwise the circuit will operate in DCM mode, exacerbate zero-crossing distortion. It is needed to improve the system current loop cut-off frequency to reduce  $\theta$ , that requires a corresponding increase in switching frequency. The switching frequency is limited by the core material, the impact of driver chips and power devices, so it can't be increased indefinitely. Both the three-level technology and parallel interleaving technology can equivalently improve switching frequency and reduce the value of inductor without increasing the switching frequency of the system<sup>[6]</sup>. Three-level technology is more complex and requires high stability of the system, so the parallel interleaving technology is used as PFC topology.

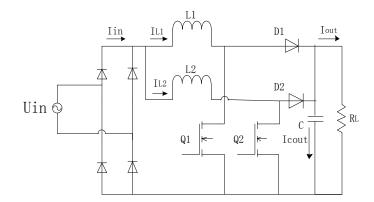

Figure 4 is the interleaved Boost PFC converter topology<sup>[7]</sup>, it consists of two identical parameters Boost PFC converter units connected in parallel, two-way switch is in accordance with the duty cycle of the driving signal frequency, interleaving conduction 180°. The input current is the sum of the two inductor current and the output current is the sum of two boost diode current.

Figure-4: The block diagram of Interleaved Boost PFC

One obvious advantage of this topology is that two-way is interleaved, thus the equivalent switching frequency is doubled. Another advantage is that each branch of the inductor ripple current value of the coefficient can be larger, and thus reduce the value of inductor. Because the two inductors are in the conduction state of interleaving, so two phase inductor ripple current also in staggered state, two superimposed ripple

current can be cancelled to reduce input current ripple. Each branch provides current rising rate unchanged, but after two superimposed itself required input current rising slope was significantly reduced. Therefore the topology of the input current is easier to track the ideal current waveform, improving the input current zero-crossing distortion effectively.

# IV. SIMULATION AND EXPERIMENTAL RESEARCH

Use simulation software TINA to simulate on the interleaved Boost PFC chip UCC28070 from TI. The experimental parameters are as follows:

- (1) Input AC voltage:  $V_{in} = 115V / 400Hz$ ;

- (2) Output DC voltage:  $V_o = 390V$ ;

- (3) Output power:  $P_o = 600W$ ;

- (4) Inductance:  $L_1 = L_2 = 280 \mu H$ ;

- (5) Switching frequency:  $f_s = 200kHz$ ;

- (6) Output capacitor:  $C_0 = 360 \mu F$ .

As can be seen from the simulation Figure 5, the input current can track the input voltage very well, the phase difference is almost zero, the cusp distortion also improved much. The introduction of parallel interleaving technique can effectively improve the zero crossing distortion problems.

Figure-5:UCC28070 input voltage and input current simulation waveform

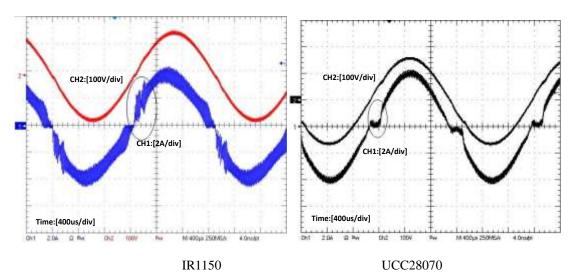

The laboratory already has a 600W Boost PFC experimental prototype which the controlling chip is IR1150, the peripheral circuit parameter: nductance L = 600uH, switching frequency  $f_s = 100kHz$ , output capacitor  $C_0 = 360uF$ .

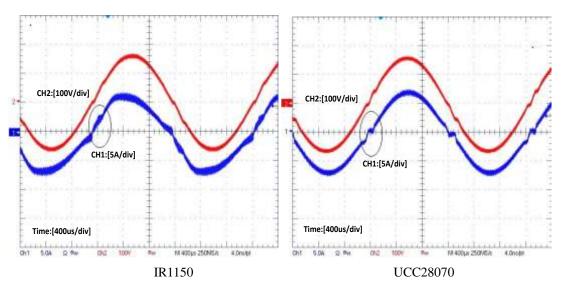

In order to verify the above analysis, the completion of a 600W interleaved Boost PFC prototype comparison, the controlling chip is UCC28070, experimental prototype parameters consistent with the simulation parameters. AC power supply box is Chroma 61504, power analyzer is Chroma 66202. Experimental waveforms are as follows:

Figure-6: The input voltage and current waveform under half load of two converters

Figure-7: The input voltage and current waveform under full load of two converters

Figures 6, 7 are given half load, full load Boost PFC converter input voltage and the input current waveform. It can be seen from the waveform, using IR1150 of Boost PFC converter input voltage crosses zero phase advance angle is large, and  $\alpha$  is also larger, it has more serious current distortion so the current ripple is larger. And after using interleaved Boost PFC converters, there is almost no phase difference and  $\alpha$  is significantly reduced, compared to the Boost PFC converter current harmonics is also greatly reduced, THD and PF values are shown in Table 1, each input current harmonics can meet the appropriate standards.

|      | PF/THD | IR1150  | UCC28070 |

|------|--------|---------|----------|

| 300W | PF     | 0.9831  | 0.9962   |

|      | THD    | 7.9390% | 4.8619%  |

| 600W | PF     | 0.9865  | 0.9949   |

|      | THD    | 8.7137% | 4.9764%  |

Table 1 The PF and THD of the two converters at half and full load

# **V. CONCLUSION**

By analyzing Boost PFC converter input current zero distortion causes, the derived solution is to reduce the value of inductor and improve higher switching frequencies. Interleaved technology because of its topological characteristics can reduce value of inductor and the equivalent switching frequency is doubled. From both simulation and experimental prototype to verify that the use of this Boost PFC converter topology can effectively improve the input current zero-crossing distortion to meet the corresponding current harmonic standards.

### **VI.** Acknowledgements

This work was financially supported by Practical Teaching Construction Project of Shanghai University of Engineering Science (p201402003).

### References

- [1] Liu Qi, Medium frequency power single phase power factor correction, Chongqin University, 2010. (7)

- [2] Aircraft Power Supply Characteristics, GJB181B-2012[S]. PLA General Armament Department, 2012(8)

- [3] Jian.Sun,On the zero-crossing distortion in single-phase PFC converters,IEEE,Trans.PowerElectron,19(11)2009,685-692.

- [4] Qu Xiaohui, Ruan Xinbo, A technique for improving input current zero-crossing distortion of single-phase PFC converter, China Electrical Engineering, 26(24), 2006, 66-71.

- [5] Ji Xiaolan, Design of multi-level PFC of 400Hz input, Nanjing University of Aeronautics and Astronautics, 2012(3).

- [6] L.Balogh,and R.Redl.Power factor correction with interleaved Boost converters in Continuous-Inductor-Current Mode,IEEE APEC,1995,434-439.

- [7] Chen Li. Research on Parallel Interleaved Boost PFC Technoloy, Southwest Jiaoatong University, 2013(7).